2020 IFIP/IEEE 28th International Conference on Very Large Scale Integration (VLSI-SOC)

时间:2020-10-05 09:00 至 2020-10-07 18:00

地点:Salt Lake City

- 会议内容

首页 > 商务会议 > 学术会议会议 > 2020 IFIP/IEEE 28th International Conference on Very Large Scale Integration (VLSI-SOC) 更新时间:2019-09-06T14:54:28

|

2020 IFIP/IEEE 28th International Conference on Very Large Scale Integration (VLSI-SOC) 已过期

会议时间:2020-10-05 09:00至 2020-10-07 18:00结束 会议地点: Salt Lake City 详细地址会前通知 None 会议规模:暂无 主办单位: IEEE Council on Electronic Design Automation IEEE Circuits and Systems Society IFIP WG10.5 |

会议内容

会议内容

VLSI-SoC 2018 is the 26thin a series of international conferences sponsored by the International Federation for Information Processing Technical Committee 10 Working Group 5, IEEE CEDA and IEEE CASS, which explore the state-of-the-art in the areas ofVery Large Scale Integration(VLSI) andSystem-on-Chip(SoC) design. The purpose of VLSI-SoC is to provide a forum to exchange ideas and showcase academic as well as industrial research in architectures, circuits, devices, design automation, verification, test, and security, within digital, analog, and mixed-signal systems.

VLSI-SoC 2018 will be held under the theme “Design and engineering of electronics systems based on new computing paradigms” by addressing cutting-edge research fields like heterogeneous, neuromorphic and brain-inspired, biologically-inspired, approximate computing systems.VLSI-SoC 2018 will be held in Verona, Italy. Verona, which has been awarded World Heritage Site status by UNESCO because of its urban structure and architecture, is the set of the Shakespeare’s Romeo and Juliet play, one of the most visited Roman imperial city in Northern Italy, the capital of the opera lyrics with its Arena roman amphitheater, the land of the Amarone della Valpolicella vineyards.

Conference Theme: “Design and Engineering of Electronics Systems Based on New Computing Paradigms“

初稿截稿日期:2020-05-01

Research topics of interest include, but are not limited to:

| TRACK 1: | Analog, mixed-signal, and sensor architectures |

| TRACK 2: | Digital architectures: NoC, multi- and many-core, hybrid, and reconfigurable |

| TRACK 3: | CAD: Synthesis and analysis |

| TRACK 4: | Prototyping, verification, modeling, and simulation |

| TRACK 5: | Circuits and systems for signal processing and communications |

| TRACK 6: | IoT, embedded and cyberphysical systems: Architecture, design, and software |

| TRACK 7: | Low-power and thermal-aware IC design |

| TRACK 8: | Emerging technologies and computing paradigms |

| TRACK 9: | Variability, reliability, and test |

| TRACK 10: | Hardware security |

| TRACK 11: | Machine learning for SoC design and for electronic design automation |

GENERAL CHAIRS

Graziano Pravadelli(University of Verona, IT)

Todd Austin(University of Michigan, USA)

PROGRAM CHAIRS

Nicola Bombieri(University of Verona, IT)

Masahiro Fujita(University of Tokyo, JP)

SPECIAL SESSION CHAIRS

Sirnivas Katkoori(University of South Florida, USA)

Katell Morin-Allory(TIMA Laboratory, FR)

PHD FORUM CHAIRS

Kiyoung Choi(Seoul National University, KOR)

Sara Vinco(Politecnico di Torino, IT)

INDUSTRIAL CHAIR

Yervant Zorian(Synopsys, USA)

LOCAL CHAIR

Franco Fummi(University of Verona, IT)

PUBLICITY CHAIRS

Ricardo Reis(UFRGS, BR)

Matteo Sonza Reorda(Politecnico di Torino, IT)

PUBBLICATION CHAIRS

Davide Bertozzi(University of Ferrara, IT)

Mahdi Tala(University of Ferrara, IT)

REGISTRATION CHAIR

Michele Lora(Singapore University of Technology and Design, SGP)

PROGRAM COMMITTEETrack 1: Analog, mixed-signal, and sensor architectures

Piero Malcovati, University of Pavia, Italy(Track Chair)

Tetsuya Iizuka, University of Tokyo, Japan(Track Chair)

Track 2: Digital architectures: NoC, multi- and many-core, hybrid, and reconfigurable

Ian O'Connor, Lyon Institute of Nanotechnology, France(Track Chair)

Michael Huebner, Ruhr-Universitat Bochum, Germany(Track Chair)

Track 3: CAD: Synthesis and analysis

Srinivas Katkoori, University of South Florida, USA(Track Chair)

Ibrahim Elfadel, Masdar Institute, UAE(Track Chair)

Track 4: Prototyping, verification, modeling, and simulation

Tiziana Margaria, Lero, Ireland(Track Chair)

Katell Morin-Allory, Grenoble Intitute of Technology, France(Track Chair)

Track 5: Circuits and systems for signal processing and communications

Fatih Ugurdag, Ozyegin University, Turkey(Track Chair)

Luc Claesen, Hasselt University, Belgium(Track Chair)

Track 6: IoT, embedded and cyberphysical systems: Architecture, design, and software

Zebo Peng, Linkoping University, Sweden(Track Chair)

Donatella Sciuto, Politecnico di Milano, Italy(Track Chair)

Track 7: Low-power and thermal-aware IC design

Dimitrios Soudris, National Technical University of Athens NTUA, Greece(Track Chair)

Alberto Macii, Politecnico di Torino, Italy(Track Chair)

Track 8: Emerging technologies and computing paradigms

Andrea Calimera, Politecnico di Torino, Italy(Track Chair)

Ricardo Reis, UFRGS, Brazil(Track Chair)

Track 9: Variability, reliability, and test

Salvador Mir, University of Grenoble Alpes, France(Track Chair)

Matteo Sonza Reorda, Politecnico di Torino, Italy(Track Chair)

Track 10: Hardware security

Mihalis Maniatakos, New York University Abu Dhabi, UAE(Track Chair)

Lilian Bossuet, University St. Etienne, France(Track Chair)

Track 11: Machine learning for SoC design and for electronic design automation

Mehdi Tahoori, Karlsruhe Institute of Technology, Germany(Track Chair)

Manuel Barragan, TIMA, France(Track Chair)

Abdulkadir Akin, ETHZ, Switzerland

Aida Todri-Sanial, LIRMM, France

Alberto Bosio, LIRMM, France

Alberto Gola, AMS, Italy

Andrea Acquaviva, Politecnico di Torino, Italy

Anupam Chattopadhyay, Nanyang Technological University, Singapore

Arun Kanuparthi, Intel, USA

Bei Yu, University of Texas at Austin, USA

Brice Colombier, CEA, France

Carlos Silva Cardenas, Pontificia Universidad Catolica del Peru, Peru

Cecile Braunstein, PMC/LIP6, France

Chengmo Yang, University of Delaware, USA

Chun-Jen Tsai, National Chiao Tung University, Taiwan

Diana Goehringer, TU Dresden, Germany

Diego Barrettino, Ecole Polytechnique Federale de Lausanne, France

Donghwa Shin, Yeungnam University, Korea

Edoardo Bonizzoni, University of Pavia, Italy

Elena Ioana Vatajelu, IMAG, France

Federico Tramarin, CNR-IEIIT, Italy

Franck Courbon, University of Cambridge, UK

Fynn Schwiegelshohn, Ruhr University Bochum, Germany

Georg Sigl, TU Munich, Germany

Gildas Leger, Instituto de Microelectronica de Sevilla IMSE-CNM-CSIC, Spain

Giorgio Di Natale, LIRMM, France

Haluk Konuk, Broadcom, USA

Haris Javaid, Xilinx, Australia

Houman Homayoun, George Mason University, USA

Ippei Akita, Toyohashi University of Technology, Japan

Iraklis Anagnostopoulos, National Technical University of Athens, Greece

Jaan Raik, Tallin University, Estonia

Jones Yudi Mori, University of Brasilia, Brasil

Jinmyoung Kim, Samsung Advaced Institute of Technology, South Korea

Johanna Sepulveda, Technical University of Munich, Germany

Jose Monteiro, INESC-ID, IST Ulisboa, Portugal

Ke Huang, San Diego State University, USA

Kostas Siozios, Aristotle University of Thessaloniki, Greece

Lars Bauer, Karlsruhe Institute of Technology, Germany

Leandro Indrusiak, University Of York, UK

Lionel Torres, LIRMM, France

Luciano Ost, University of Leicester, UK

Maksim Jenihhin, Tallinn University of Technology, Estonia

Maria Michael, University of Cyprus, Cyprus

Massimo Poncino, Politecnico di Torino, Italy

Matthias Sauer, University Freiburg

Mirko Loghi, Università di Udine, Italy

Nadine Azemard, LIRMM / CNRS, France

Nele Mentens, Katholieke Universiteit Leuven, Belgium

Nektarios Georgios Tsoutsos, New York University, USA

Ozgur Tasdizen, ARM, UK

Paolo Amato, Micron, Italy

Patri Sreehari, National Institute of Technology, Warangal, India

Peng Liu, Zhejiang University, China

Per Larsson-Edefors, Chalmers University, Sweden

Philippe Coussy, University De Bretagne, France

Pierre-Emmanuel Gaillardon, University of Utah, USA

Po-Hung Chen, National Chiao Tung University, Taiwan

Raik Brinkmann, OneSpin Solutions, Germany

Rani S. Ghaida, GlobalFoundries, USA

Robert Wille, Johannes Kepler University Linz, Austria

Rouwaida Kanj, American University Of Beirut, Libano

Said Hamdioui, Delf Technical University, The Netherland

Salvatore Pennisi, University of Catania, Italy

Sezer Goren, Yeditepe University, Turkey

Shahar Kvatinsky, Technion - Israel Institute of Technology, Israel

Sicheng Li, HP, USA

Soheil Samii, General Motors, USA

Sri Parameswaran, University of New South Wales, Australia

Tetsuya Hirose, Kobe University, Japan

Theocharis Theocharides, University of Cyprus, Cyprus

Tolga Yalcin, NXP, UK

Valerio Tenace, Politecnico di Torino, Italy

Victor Champac, National Institute or Astrophysics, Optics and Electronics, Mexico

Victor Kravets, IBM, USA

Virendra Singh, Indian Institute of Technology Bombay, India

Vladimir Zolotov, IBM, USA

Wenjing Rao, University of Illinois at Chicago, USA

Yier Jin, University of Florida, USA

- - Manfred Glesner, TU Darmstadt, Germany

- - Matthew Guthaus, UC Santa Cruz, USA

- - Luis Miguel Silveira, INESC ID, Portugal

- - Fatih Ugurdag, Ozyegin University, Turkey

- - Salvador Mir, TIMA, France

- - Ricardo Reis, UFRGS, Brazil

- - Chi-Ying Tsui, HKUST, Hong Kong, China

- - Ian O'Connor, INL, France

- - Masahiro Fujita, The University of Tokyo, Japan

声明:

1、以上会议非活动家网站主办或承办会议,活动家网站学术会议频道会议信息来自于互联网,方便用户了解行业信息,如需参会、报名、获取会议邀请函或会议日程,请直接与学术会议活动主办单位联系。

2、部分会议内容来自互联网,由于网络的不确定性,活动家网站对所发布的信息不承担真实性的鉴别工作,请谨慎选择。若您发现会议页面信息有误,请联系活动家客服028-69761252纠错。

查看更多

介绍:IEEE Council on Electronic Design Automation于2020年10月5日举办2020 IFIP/IEEE 28th International Conference on Very Large Scale Integration (VLSI-SOC)。

主办方:IEEE Circuits and Systems Society介绍:IEEE Circuits and Systems Society于2020年10月5日举办2020 IFIP/IEEE 28th International Conference on Very Large Scale Integration (VLSI-SOC)。

主办方:IFIP WG10.5介绍:IFIP WG10.5于2020年10月5日举办2020 IFIP/IEEE 28th International Conference on Very Large Scale Integration (VLSI-SOC)。

温馨提示

酒店与住宿:

为防止极端情况下活动延期或取消,建议“异地客户”与活动家客服确认参会信息后,再安排出行与住宿。

退款规则:

活动各项资源需提前采购,购票后不支持退款,可以换人参加。

您可能还会关注

您可能还会关注

-

AiCon北京2025|全球人工智能与大模型应用峰会·12月

2025-12-19 北京

-

AI Maker Summit 2025 北京

2025-12-14 北京

-

AI+创新科技大会:AI+营销论坛

2025-11-28 上海

-

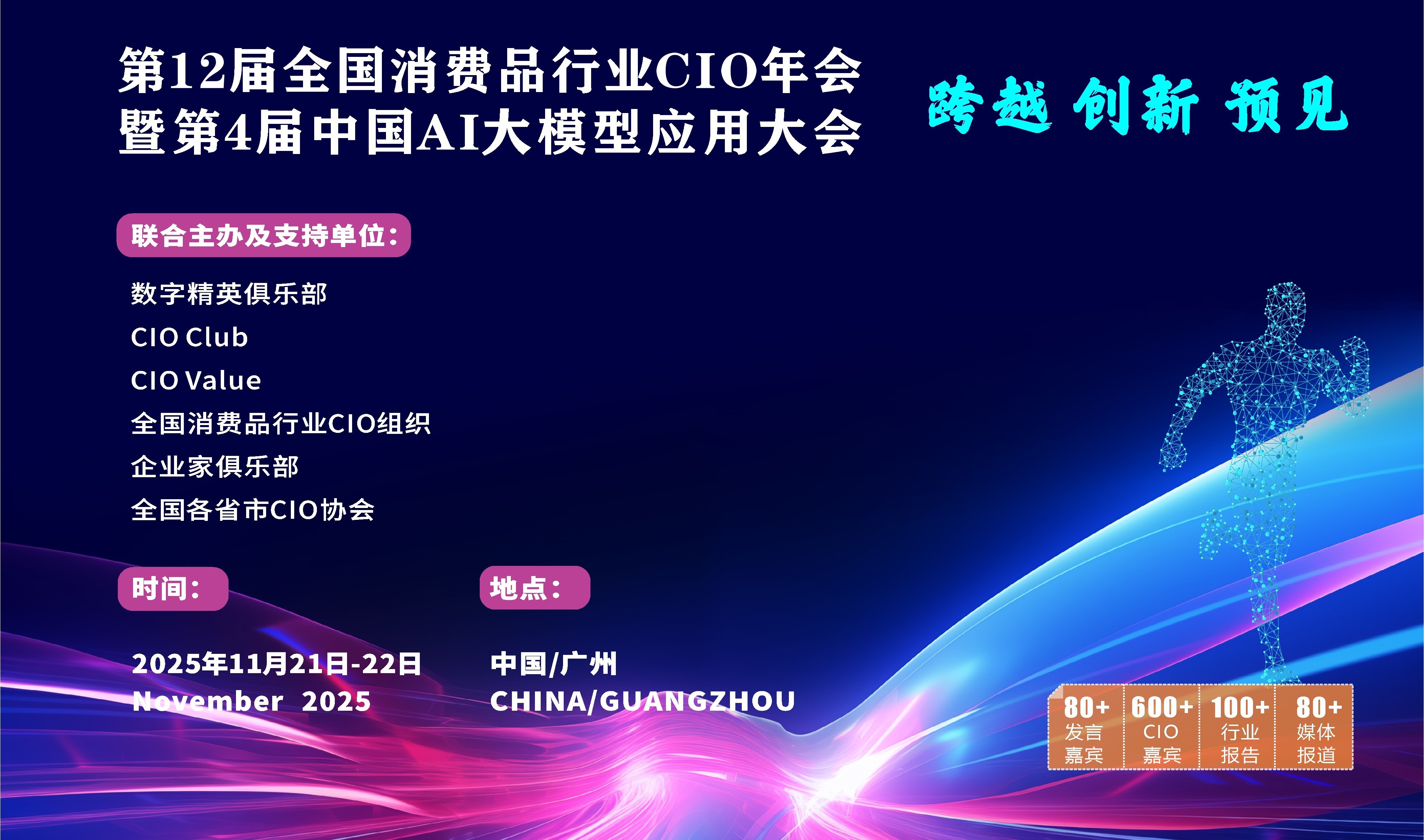

第12届全国消费品行业CIO年会暨中国第4届AI大模型应用大会

2025-11-21 广州

部分参会单位

邮件提醒通知

.png)

赞助

赞助